# Clock generator for digital still camera BU2382FV

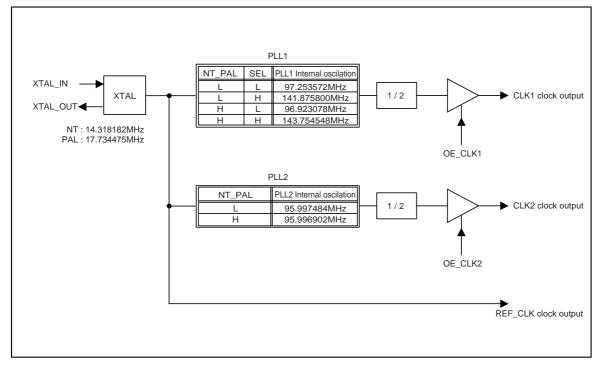

BU2382FV is a high-performance 2-channel PLL IC. PLL circuit generates necessary clocks by inputting standard clocks of crystal oscillator from outside. Changing a connection of wire can generate any clocks required for any applications of users. Jitter and S/N characteristic has achieved almost the same high-quality sound and vision as oscillating module because of optimization of PLL. Frequency can be changed by the internal dividing control.

#### Applications

Digital still camera

#### Features

- 1) Generate clocks for CDS, USB with standard clock input

- 2) No external elements required

- 3) Standard clocks apply to two kinds of NTSC/PAL

- 4) Power down control in each 2-channel PLL

- 5) Single power supply of 3.3V operating

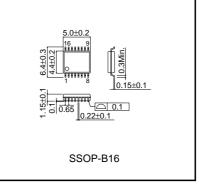

- 6) SSOP-B16 small package

#### Absolute maximum ratings (Ta=25°C)

| Parameter                 | Symbol | Limits          | Unit |

|---------------------------|--------|-----------------|------|

| Applied voltage           | Vdd    | -0.5 to +7.0    | V    |

| Input voltage             | Vin    | -0.5 to VDD+0.5 | V    |

| Storage temperature range | Tstg   | -30 to +125     | °C   |

| Power dissipation         | Pd     | 450             | mW   |

\*IC destruction is not occurred, however, operation can not be guaranteed.

\*Derating : 4.5mW/°C for operation above Ta=25°C.

\*This product is not designed for protection against radioactive rays.

\*Power dissipation is the rate when the IC is mounted on the board.

Recommended operating conditions (Ta=25°C)

| Parameter               | Symbol | Min.   | Тур. | Max.   | Unit |

|-------------------------|--------|--------|------|--------|------|

| Power supply voltage    | Vdd    | 3.0    | -    | 3.6    | V    |

| Input "H" voltage range | VIH    | 0.8Vdd | -    | Vdd    | V    |

| Input "L" voltage range | VIL    | 0      | -    | 0.2Vdd | V    |

| Operating temperature   | Topr   | -5     | _    | +70    | °C   |

| Output load             | CL     | _      | _    | 15     | pF   |

# BU2382FV

# Multimedia ICs

#### •Block diagram

| NT_PAL | SEL | REF–CLK (MHz)                                 | CLK1 (MHz) | CLK2 (MHz)                        |  |

|--------|-----|-----------------------------------------------|------------|-----------------------------------|--|

| L      | L   | L 17.734475 48.626786<br>XTAL * (170 / 31) /2 |            | 47.998742<br>XTAL * (249 / 46) /2 |  |

| L      | н   | H 17.734475 70.937900<br>XTAL * (360 / 45) /2 |            | 47.998742<br>XTAL * (249 / 46) /2 |  |

| Н      | L   | 14.318182 48.461539<br>XTAL * (176 / 26) /2   |            | 47.998451<br>XTAL * (295 / 44) /2 |  |

| Н      | Н   | H 14.318182 71.877274<br>XTAL * (502 / 50) /2 |            | 47.998451<br>XTAL * (295 / 44) /2 |  |

# BU2382FV

# Multimedia ICs

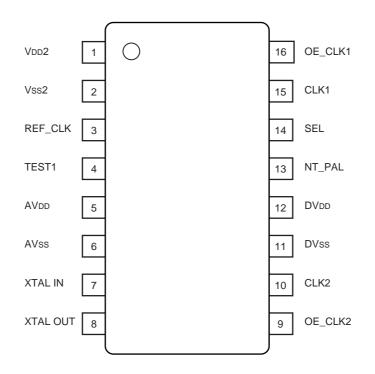

#### •Pin descriptions

| Pin No. | Pin name | Functions                                                   |  |  |

|---------|----------|-------------------------------------------------------------|--|--|

| 1       | Vdd2     | VDD for clock output                                        |  |  |

| 2       | Vss2     | GND for clock output                                        |  |  |

| 3       | REF_CLK  | Crystal output                                              |  |  |

| 4       | TEST1    | Test mode control pin                                       |  |  |

| 5       | AVdd     | Analog VDD                                                  |  |  |

| 6       | AVss     | Analog GND                                                  |  |  |

| 7       | XTALIN   | Standard crystal input                                      |  |  |

| 8       | XTALout  | Standard crystal output                                     |  |  |

| 9       | OE_CLK2  | Output enable pin for CLK2 (H : enable, L : output L fixed) |  |  |

| 10      | CLK2     | CLK2 clock output                                           |  |  |

| 11      | DVss     | Digital GND                                                 |  |  |

| 12      | DVdd     | Digital VDD                                                 |  |  |

| 13      | NT_PAL   | NT / PAL select (L : PAL, H : NTSC)                         |  |  |

| 14      | SEL      | Output select                                               |  |  |

| 15      | CLK1     | CLK1 clock outpt                                            |  |  |

| 16      | OE_CLK1  | Output enable pin for CLK1 (H : enable, L :output Lfixed)   |  |  |

# Multimedia ICs

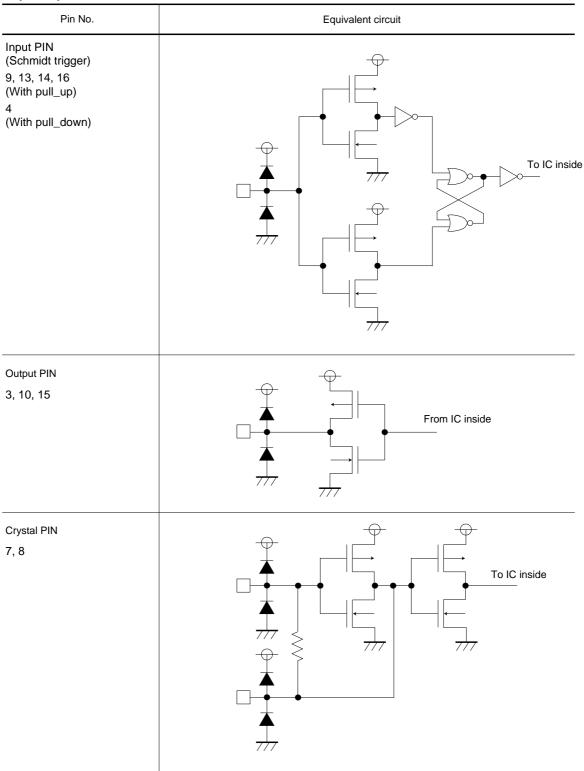

### •Input output circuits

# BU2382FV

# Multimedia ICs

| Parameter                 | Symbol                                   | Min.   | Тур.                                             | Max.   | Unit | Conditions                                                                                                                                           |

|---------------------------|------------------------------------------|--------|--------------------------------------------------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output H voltage          | VOH                                      | 2.4    | -                                                | -      | V    | IOH=4.0mA                                                                                                                                            |

| Output L voltage          | VOL                                      | -      | -                                                | 0.4    | V    | IOL=4.0mA                                                                                                                                            |

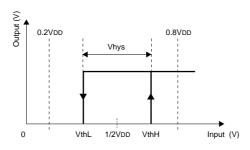

| Input VthL *3             | VthL                                     | 0.2Vdd | -                                                | -      | V    | *1                                                                                                                                                   |

| Input VthH *3             | VthH                                     | -      | -                                                | 0.8Vdd | V    | *1                                                                                                                                                   |

| Hysteresis width *3       | Vhys                                     | -      | 0.4                                              | -      | V    | Vhys=VthH-VthL                                                                                                                                       |

| Operating circuit current | IDD                                      | -      | 30                                               | 45     | mA   | No load                                                                                                                                              |

| CLK1                      | CLK1_LL<br>CLK1_LH<br>CLK1_HL<br>CLK1_HH | -      | 48.626786<br>70.937900<br>48.461539<br>71.877274 | _      | MHz  | XTAL *170/31/2 (XTAL=17.734475MHz)<br>XTAL *360/45/2 (XTAL=17.734475MHz)<br>XTAL *176/26/2 (XTAL=14.318182MHz)<br>XTAL *502/50/2 (XTAL=14.318182MHz) |

| CLK2                      | CLK2_L<br>CLK2_H                         | -      | 47.998742<br>47.998451                           | _      | MHz  | XTAL *249/46/2 (XTAL=17.734475MHz)<br>XTAL *295/44/2 (XTAL=14.318182MHz)                                                                             |

| Duty                      | Duty                                     | 45     | 50                                               | 55     | %    | 1/2 Vpd test                                                                                                                                         |

| Jitter 1σ                 | JsSD                                     | -      | 30                                               | -      | psec | $1\sigma$ short time jitter                                                                                                                          |

| Jitter MIN-MAX            | JsABS                                    | -      | 180                                              | -      | psec | MINMAX.                                                                                                                                              |

| Rise time                 | tr                                       | -      | 2.5                                              | -      | nsec | 20% to 80% time of VDD                                                                                                                               |

| Fall time                 | tf                                       | -      | 2.5                                              | -      | nsec | 20% to 80% time of VDD                                                                                                                               |

| Output Lock time          | tlock                                    | -      | _                                                | 1      | msec | *2                                                                                                                                                   |

### •Electrical characteristics (Unless specified otherwise Ta=25°C, VCC=3.3V, crystal frequency=14.318182MHz )

Note) Output frequency is determined by the operation expression (Frequency divide) input to XTAL IN. Output at 27MHz input is shown above. Jitter is value when using Time interval analyzer with 10000 sampling.

\*1) Low and high limit voltage in the schmitt trigger input Pin having hysteresis features shown in \*3 diagram.

\*2) Time that output takes to stabilize in the specific frequency range after the power supply reaches to 3.0V.

\*3) Make reference to the diagram.

# **Multimedia ICs**

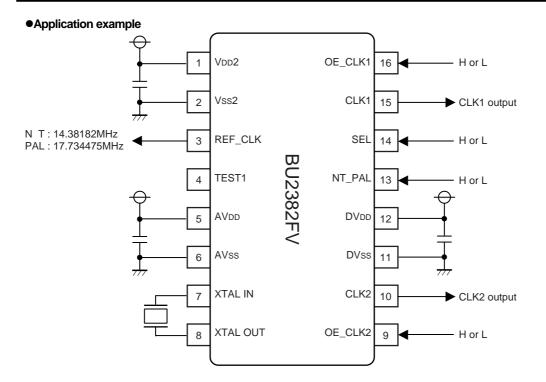

Note) The BU2382FV is basically placed on the board.

Decoupling capacitance ( $0.1\mu$ F) need to be placed between Pin1 (VDD2) and Pin2 (Vss2), Pin5 (AVDD) and Pin6 (AVss), Pin11 (DVss) and Pin12 (DVDD).

To obtain accurate frequency, capacitance (pF) need to be placed between Pin8 (XTAL IN) and Pin6 (AVss). Pin7 (XTAL OUT) and Pin6 (AVss).

Tantalum capacitance (10 to  $100\mu$ F), ferrite beads may need to be placed to prevent power supply drop in certain board's case.

To reduce high frequency noise, selected bypass capacitors (<1 $\Omega$  at problem high frequency) maybe used for power pin as close to BU2382FV as possible.

#### Notes

- No technical content pages of this document may be reproduced in any form or transmitted by any means without prior permission of ROHM CO.,LTD.

- The contents described herein are subject to change without notice. The specifications for the product described in this document are for reference only. Upon actual use, therefore, please request that specifications to be separately delivered.

• Application circuit diagrams and circuit constants contained herein are shown as examples of standard use and operation. Please pay careful attention to the peripheral conditions when designing circuits and deciding upon circuit constants in the set.

Any data, including, but not limited to application circuit diagrams information, described herein are intended only as illustrations of such devices and not as the specifications for such devices. ROHM CO.,LTD. disclaims any warranty that any use of such devices shall be free from infringement of any third party's intellectual property rights or other proprietary rights, and further, assumes no liability of whatsoever nature in the event of any such infringement, or arising from or connected with or related to the use of such devices.

• Upon the sale of any such devices, other than for buyer's right to use such devices itself, resell or otherwise dispose of the same, no express or implied right or license to practice or commercially exploit any intellectual property rights or other proprietary rights owned or controlled by

- ROHM CO., LTD. is granted to any such buyer.

- Products listed in this document use silicon as a basic material.

Products listed in this document are no antiradiation design.

The products listed in this document are designed to be used with ordinary electronic equipment or devices (such as audio visual equipment, office-automation equipment, communications devices, electrical appliances and electronic toys).

Should you intend to use these products with equipment or devices which require an extremely high level of reliability and the malfunction of with would directly endanger human life (such as medical instruments, transportation equipment, aerospace machinery, nuclear-reactor controllers, fuel controllers and other safety devices), please be sure to consult with our sales representative in advance.

About Export Control Order in Japan

Products described herein are the objects of controlled goods in Annex 1 (Item 16) of Export Trade Control Order in Japan.

In case of export from Japan, please confirm if it applies to "objective" criteria or an "informed" (by MITI clause) on the basis of "catch all controls for Non-Proliferation of Weapons of Mass Destruction.